技术背景

目前主流的cpo有两种技术方案和应用场景。

基于vcsel的多模方案,30m及以下距离,主要面向超算及ai集群的短距光互联;

基于硅光集成的单模方案,2km及以下距离,主要面向大型数据中心内部光互联。

单波100g vcsel芯片产业成熟度比硅光子稍慢,目前n×100g vcsel array芯片(主要模块产品800g sr8)价格仍处在高位水平;

一部分数据中心终端客户希望用硅光向下覆盖短距vcsel的应用; 同时vcsel芯片制造商和交换机厂商也在继续发力,开发vcsel的低成本cpo凯发k8国际手机app下载的解决方案,以维持vcsel方案在cpo赛道的市场占有率。

本报告收集汇总了ofc2023上基于vcsel的cpo进展。

在ofc2023上,ibm介绍了基于vcsel阵列的cpo最新进展,

目前大部分cpo产品都是基于硅光的方案,但是vcsel在超短距传输上有着明显的成本与功耗优势。目前从事基于vcsel cpo研发的机构主要有:

- ibm

- hp

- fujitsu

- furukawa

这四家公司。

【玩家1】ibm

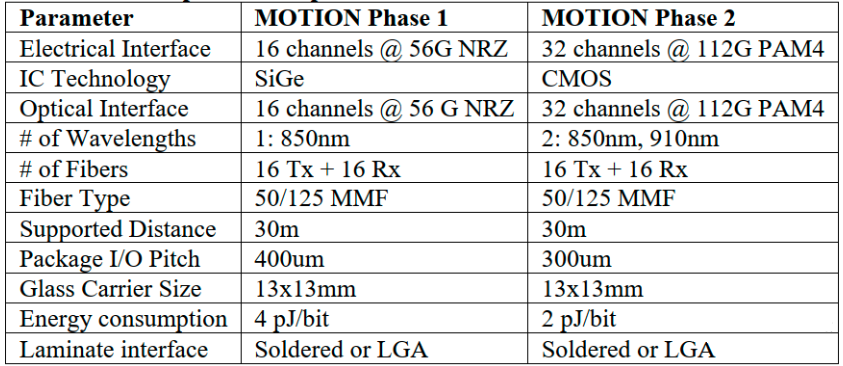

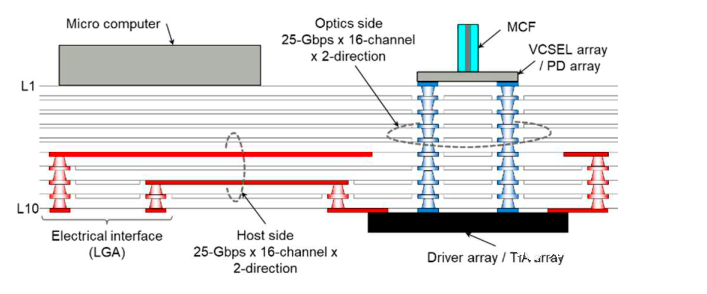

ibm与ii-vi合作,一起承接了美国能源部(arpa-e)的项目,项目的名称是motion (全称multi-wavelength optical transceiver integrated on node)。项目分为phase 1和phase 2两个阶段,两个阶段的指标如下图所示,主要区别是通道数、速率和电芯片等。cpo模块的尺寸保持不变。

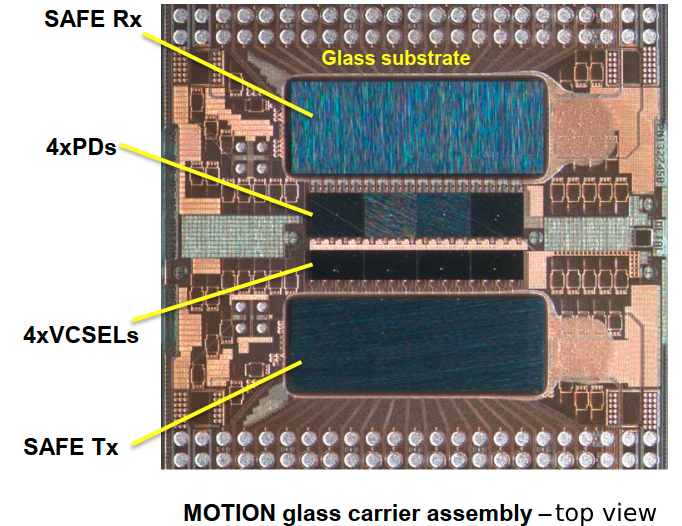

vcsel的波长为940nm,速率可以达到56gbaud, 可以支持112gbps pam4的信号。pd也是类似的情况,速率可以达到56gbaud。phase 1中的电芯片采用55nm bicmos工艺,tx和rx是单独的两颗芯片,16通道。芯片尺寸都是1.64mm*4.64mm。电芯片中没有retiming功能,因此可以支持低延迟的应用场景。电芯片、vcsel和pd芯片分别flip-chip到玻璃基板上,如下图所示

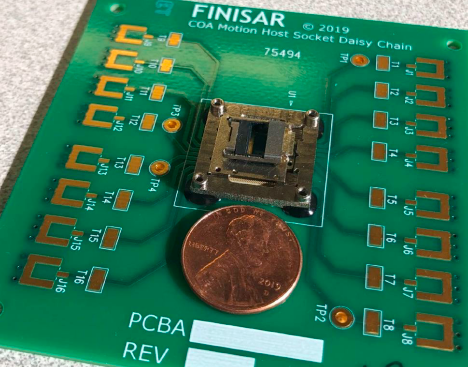

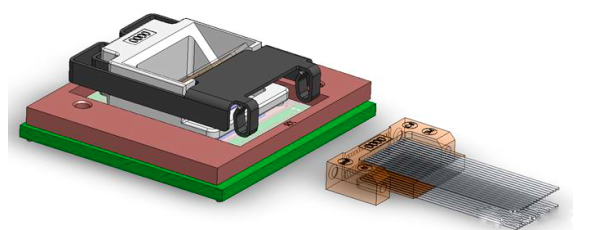

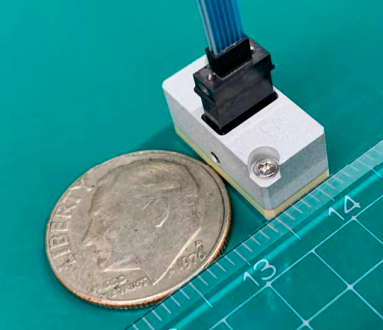

将透镜等光学元件封装在一起之后,整体模块的尺寸为13mm*13mm,和硬币的尺寸相当,如下图所示

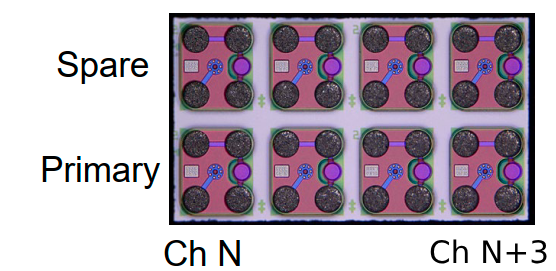

值得一提的是,考虑到cpo距离switch芯片比较近,vcsel的性能可能会有所影响。ibm在系统上放了冗余的vcsel, 如下图所示,整个系统的可靠性提升了1000倍。如果primary vcsel发生故障,可以快速切换到spare通道。

ibm没有展示太多的full-link结果,只给出了16个通道的vcsel眼图。tx端的能效比为2.7pj/bit, 包含vcsel的功耗在内。rx端没有给出实测的能效比,理论仿真值为1.5pj/bit, 整个系统的能效比4.2pj/bit。整个系统的带宽为800gbps(16x50gbps)。此外系统采用的是单波长vcsel,phase 2会引入多波长。

【玩家2】hp

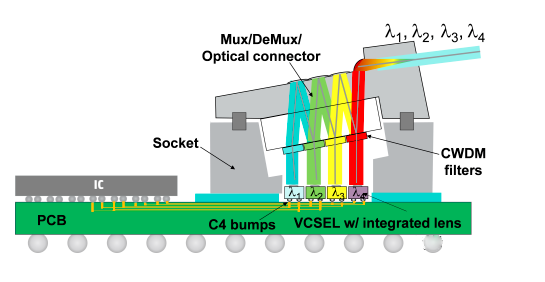

惠普也一直致力于基于vcsel的cpo研发,找到了2020年4通道cpo的文章。系统的结构如下图所示,

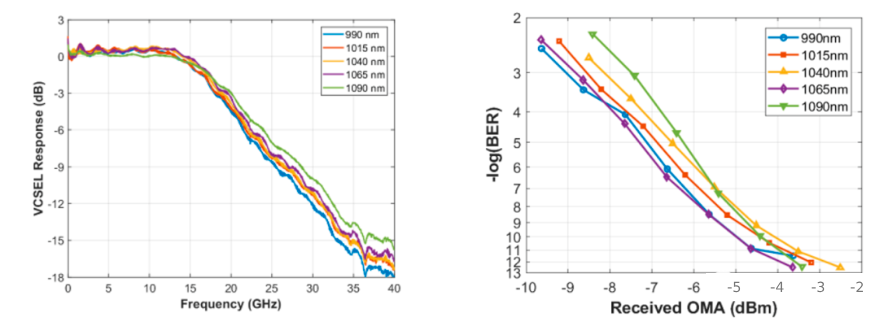

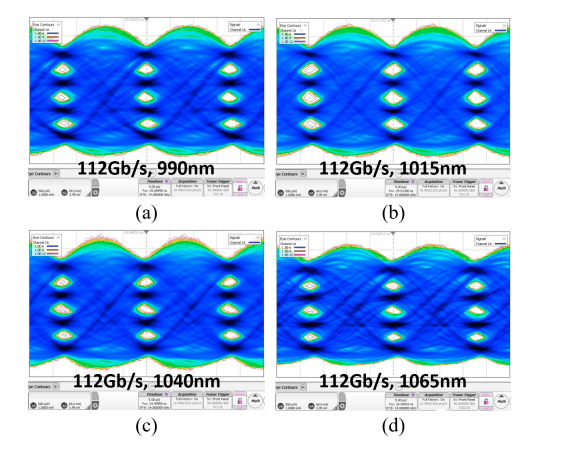

系统中含5个波长的vcsel激光器,波长分别为990/1015/1040/1065/1090nm。5个波长的3db带宽都大于18ghz, 可以支持56gbps pam4的信号,如下图所示。990nm的vcsel带宽略低。通过采用预矫正(pre-distorted)的电信号,以及增加驱动电流的大小,vcsel可以支持112gbps pam4的信号。

将vcsel阵列、pd阵列和薄膜滤波片组装在一起,构成四波长的cpo模块。由于pd无法和tia芯片匹配,hp采用了外置的探测器。cpo模块没有集成电芯片。cpo tx端的眼图如下图所示,误码率小于1e-6。

【玩家3】 fujitsu

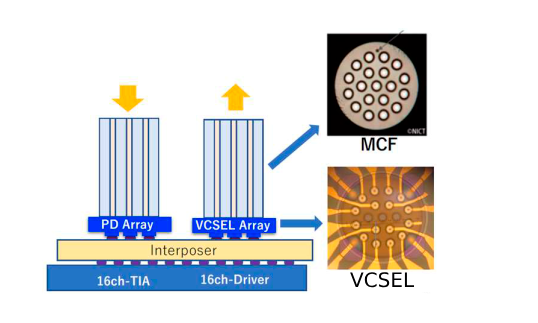

fujitsu公司的vcsel cpo方案如下图所示,系统中使用16通道的vcsel和pd阵列,为了方便与多芯光纤(mcf)耦合,vcsel和pd呈圆弧形分布,相邻通道的距离为40um。vcsel为单模1060nm输出。driver和tia芯片放置在interposer的背面。

cpo模块采用lga的电接口,pitch为300um。为了实现高速电信号的互联,interposer采用了10层金属,整个interposer的厚度为340um。其截面如下图所示,光芯片和电芯片都是采用flip-chip的方式放置在interposer上。

整体的cpo模块尺寸为7.8*16*8.0mm,也是与硬币尺寸相当,如下图所示。cpo模块的带宽为400gbps(25gbps nrz*16)。fujitsu没有给整个link的实测结果。

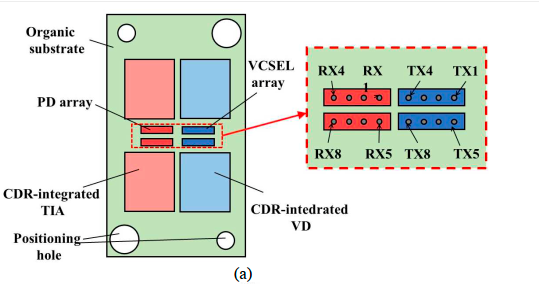

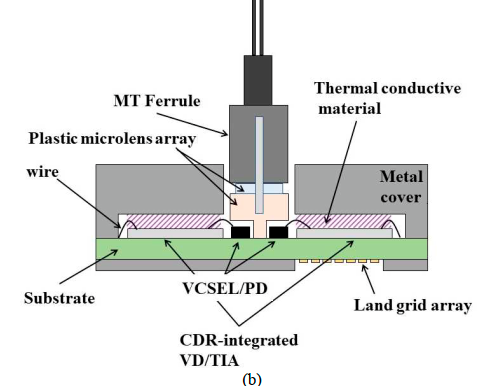

【玩家4】 furukawa

furukawa公司的vcsel cpo方案如下图所示,采用两组4通道的vcsel与pd阵列。为了减小电信号互联的长度,driver和tia芯片分别放置在vcsel和pd的两侧。光芯片和电芯片都是直接贴到substrate上,光芯片和电芯片之间采用wire-bonding的方式互联。cpo模块采用lga的电接口形式,lga的pitch也是300um。光口采用mt头,包含24个通道。

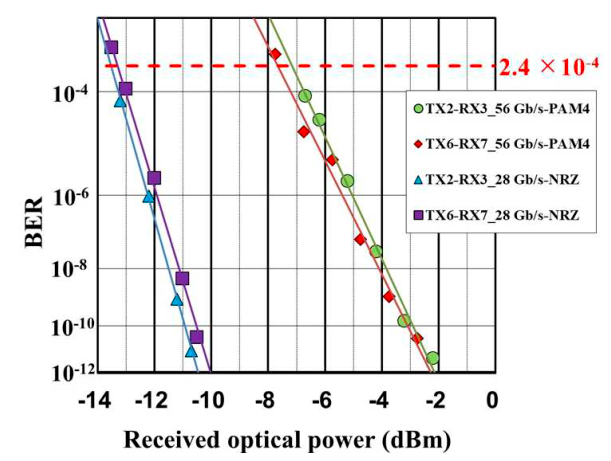

vcsel的3db带宽为17ghz, pd的3db带宽为23ghz, 都可以支持56gbps pam4的信号。 furukawa搭建了4.4m长的链路,ber的测试结果如下图所示,对于28gbps nrz信号,rx端光功率大于-10dbm,ber小于1e-12, 对于56gbps pam4信号,rx端光功率需大于-8dbm, ber小于2.4e-4。

cpo模块的尺寸为15.9*7.7*7.95mm, 总带宽为448gbps(56x8), 对应的带宽密度为7.32gbps/mm^2 (双向)。

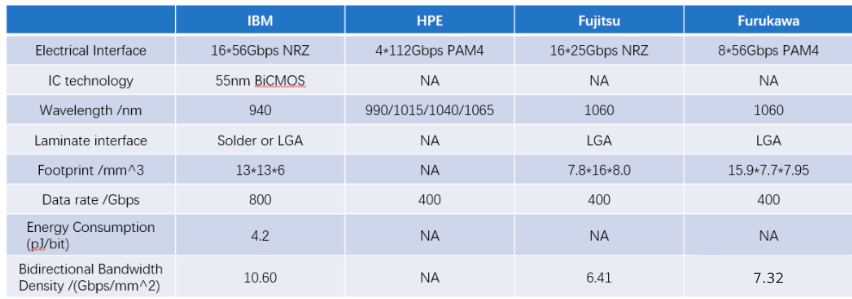

上述四家公司的结果,简单对比下,如下图所示:

小结:

相比较而言,ibm的vcsel cpo各方面的性能占优,其电芯片也是自己专门设计研发的。

而另外三家公司的文章中并没有透露太多driver/tia的信息。

四家公司的vcsel cpo都还处于研发阶段,full link的性能表征也不是很完善。vcsel cpo难点主要在封装上,四家公司的封装方案有些共性,光引擎都是采用lga的方式与pcb板互联,driver与tia都是尽量靠近vcsel与pd。另外由于系统中含有多通道的vcsel与pd, 其可靠性与维护受到了挑战。后续如何进行带宽的升级,也值得思考。由于vcsel的传输距离比较短,vcsel cpo可能主要应用在rack内和rack间的信号互联。